- #ADDER VERILOG TESTBENCH FULL ADDER VERILOG#

- #ADDER VERILOG TESTBENCH HOW TO WRITE CODE#

- #ADDER VERILOG TESTBENCH CODE IN A#

Adder Verilog Testbench Code In A

In “ Introduction to Verilog” we have mentioned that it is a good practice to write modules for each block. This tutorial focuses on writing Verilog code in a hierarchical style. So, the first step is to declare the ‘Fields‘ in the transaction class. Transaction class can also be used as a placeholder for the activity monitored by the monitor on DUT signals. ‘ADDER’ TestBench Without Monitor, Agent and Scoreboard TestBench Architecture Transaction Class Fields required to generate the stimulus are declared in the transaction class.

Adder Verilog Testbench Full Adder Verilog

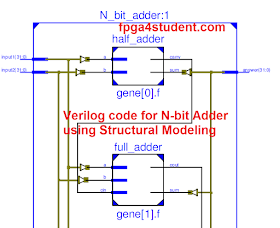

Half adder.Bottom-Up Methodology: In this approach, we first identify small blocks that are available to us and use them to construct a big block. You want to construct full adder, so you immediately identify two small blocks i.e. We further divide the small block to leaf cells which cannot be further divided. To compile and visualise the waveforms (using iverilog and gtkwave), follow these steps: Install iverilog and gtkwave using the instructions given here.Top-Down Methodology: In Top-Down we first identify or define the big circuit or big block and then identify a small block used to make this big block. To divide the big complex circuit into smaller modules and further dividing these modules to even smaller modules like gates etc.Full Adder Verilog design module fulladder(input a,b,cin, output reg sum,cout) always () begin sum abcin cout (a&b)+(b&cin)+(cin&a) end endmodule TestBench module tbfulladder reg A,B,CIN wire SUM,COUT fulladder FA (.a(A) .b(B).sum(SUM).cin(CIN).cout(COUT)) initial begin A 1b0 B 1b0 CIN 1b0 There are two design approaches when writing code in hierarchical styleFull Adder (fulladder.v) File serialadder.v is the master node, the corresponding testbench is serialaddertb.v. The key idea is to divide and conquer i.e.

An instance is a copy of a module created when a big component calls a smaller component. They build higher-level cells by using these leaf cells.Instance: Before proceeding towards examples, we would like to clarify the concept of “instance”. At the same time, circuit designers are designing optimized circuits for leaf-level cells. Logic designers decide how the design should be structured by breaking up the functionality into blocks and sub-blocks. Design architects define the specifications of the top-level block.

Adder Verilog Testbench How To Write Code

Fcarry_out(t_out_carry)) The above code is simulated in Modelsim and below are the simulated result:The above result shows the correct working of the Full adder as provided in the truth table.These two examples are the basic guidelines on how to write code in a hierarchical style.See Design of 4×2 Multiplexer using three 2×1 muxes.If you have any suggestions or questions regarding the understanding of these two examples please write in the comment section below. This will create two instance of the same module.Full_adder_join my_full_adder(.a(t_a). Note that we have called half adder 2 times as shown in block diagram as well. A block diagram for this is shown below:By using hierarchical style coding we can construct full adder using two half adder as shown in the block diagram aboveModule full_adder_join(fsum, fcarry_out, a, b, c) Wire half_sum_1, half_carry_1, half_carry_2 Half_adder HA1(half_sum_1, half_carry_1, a, b) //instance 1 of Half AdderHalf_adder HA2(fsum, half_carry_2, half_sum_1, c) //instance 2 of Half AdderOr or1(fcarry_out, half_carry_2, half_carry_1) Where half adders code are already mentioned in Example-1. The following examples will help you clarify the concept of instantiation and hierarchical designing.Example-1: Design and simulate Half-Adder using gate-level modelling.Truth Table: Given below is the truth table for half adder: InputFrom the above table of Half adder we can construct its boolean expression given below:\(\text\)As we can clearly see from boolean expressions that full adder can be constructed by using two half adders.

0 kommentar(er)

0 kommentar(er)